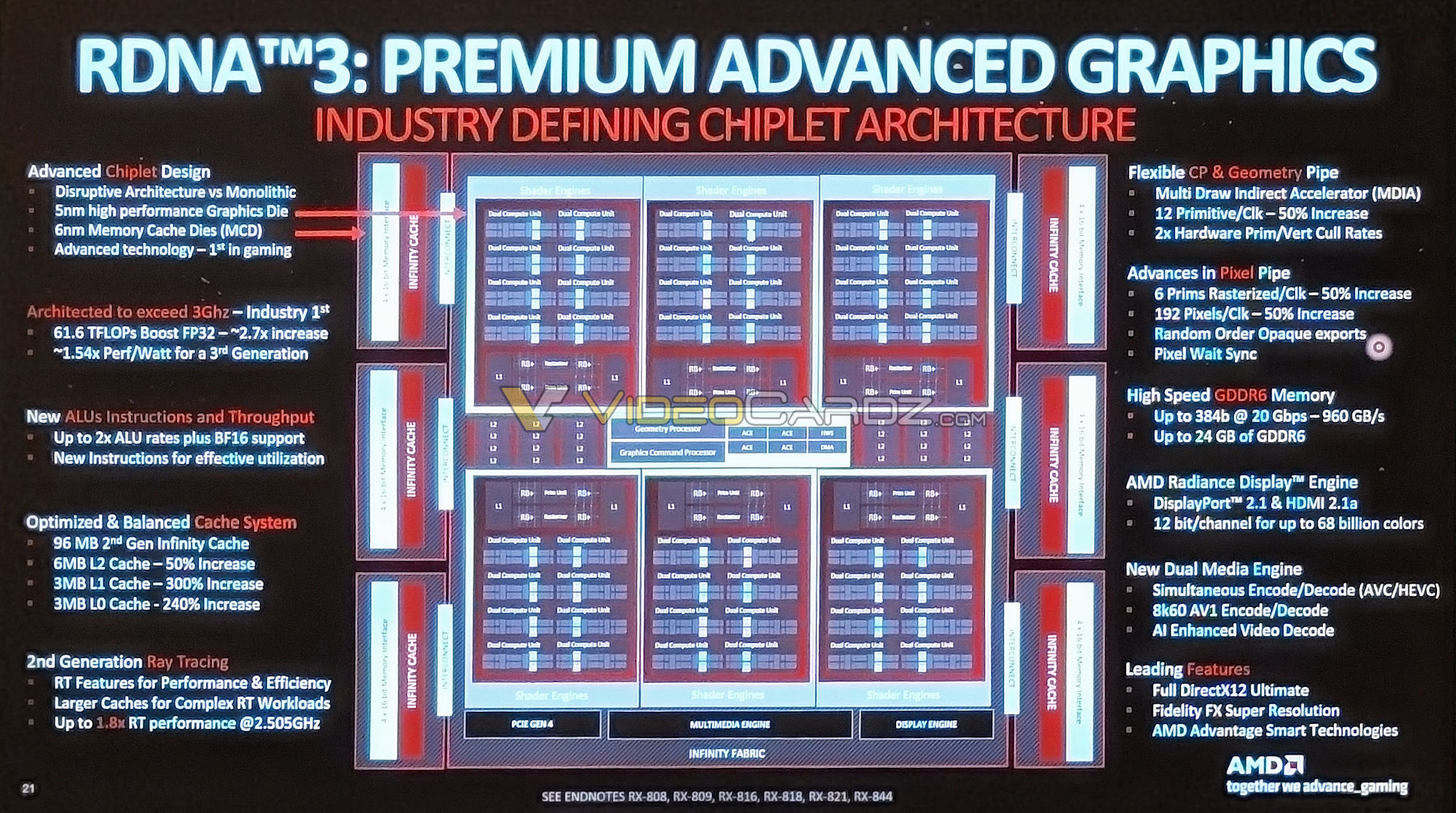

Videocardz managed to obtain a leaked block diagram of AMD’s top-of-the-line Navi31 GPU from the RDNA3 lineup. AMD unveiled the RX 7900 XTX and the RX 7900 XT based on the RDNA3 architecture 2 days ago. These GPUs are tipped to offer almost 50-70% better performance than RDNA2 while costing nearly similar.

Block Diagram for Navi31

The leaked diagram for AMD’s Navi31 shows a 6 Shader Engine layout, each packed with 8 dual Compute Units. This amounts up to 96 Compute Units for the Navi31 or 48WGPs. If we do the math, each Compute Unit in RDNA3 is equipped with 64 Shading Units, contrary to the 128 Shading Unit/CU metric we obtained before.

Core Count Confusion

Team red has used a dual-issue SIMD design for their Compute Units with RDNA3. This has caused a lot of confusion regarding the actual core count. As per AMD, the RX 7900 XTX (Full-fat Navi31) has 6144 SPs (Stream Processors/FP32 Units), although various media outlets say otherwise.

RDNA3 can basically execute two FP32 operations at the same time, as compared to one. The core count does not ‘double’ due to this inclusion. So the uplift from generation-to-generation is just 20% (5120SPs vs 6144SPs). The dual operation execution technique isn’t as effective as actual 2x more physical cores. Still, that’s also the reason why the actual performance increment is actually higher than 20%.

Cache & 3GHz Design

Aside from that, the Navi31 GPU ships with 96MB of Infinity Cache. This number was not mentioned by AMD before. The L2 cache stands at 6MB, being a 50% increase. Whereas the L1 and L0 cache values are both 3MB, offering a 300% and a 240% increase respectively.

The most noteworthy point here is that the slide states RDNA3 is ‘architected to exceed 3GHz‘. This is in-line with previous rumours, though claims contradicting this have also surfaced. Read more about that here.

Specifications For Navi31

The Navi31, codenamed ‘Plum Bonito‘ features a 1xGCD + 6xMCD design along with a maximum of 48WGPs. The Angstronomics leak, thus far has proven to be correct, apart from the ALU count.

- gfx1100 (Plum Bonito)

- Chiplet – 1x GCD + 6x MCD (0-hi or 1-hi)

- 48 WGP (96 legacy CUs, 12288 ALUs)

- 6 Shader Engines / 12 Shader Arrays

- Infinity Cache 96MB (0-hi), 192MB (1-hi)

- 384-bit GDDR6

- GCD on TSMC N5, ~308 mm²

- MCD on TSMC N6, ~37.5 mm²

The post Block Diagram For AMD’s Navi31 GPU Leaks Out appeared first on Appuals.com.

0 Commentaires